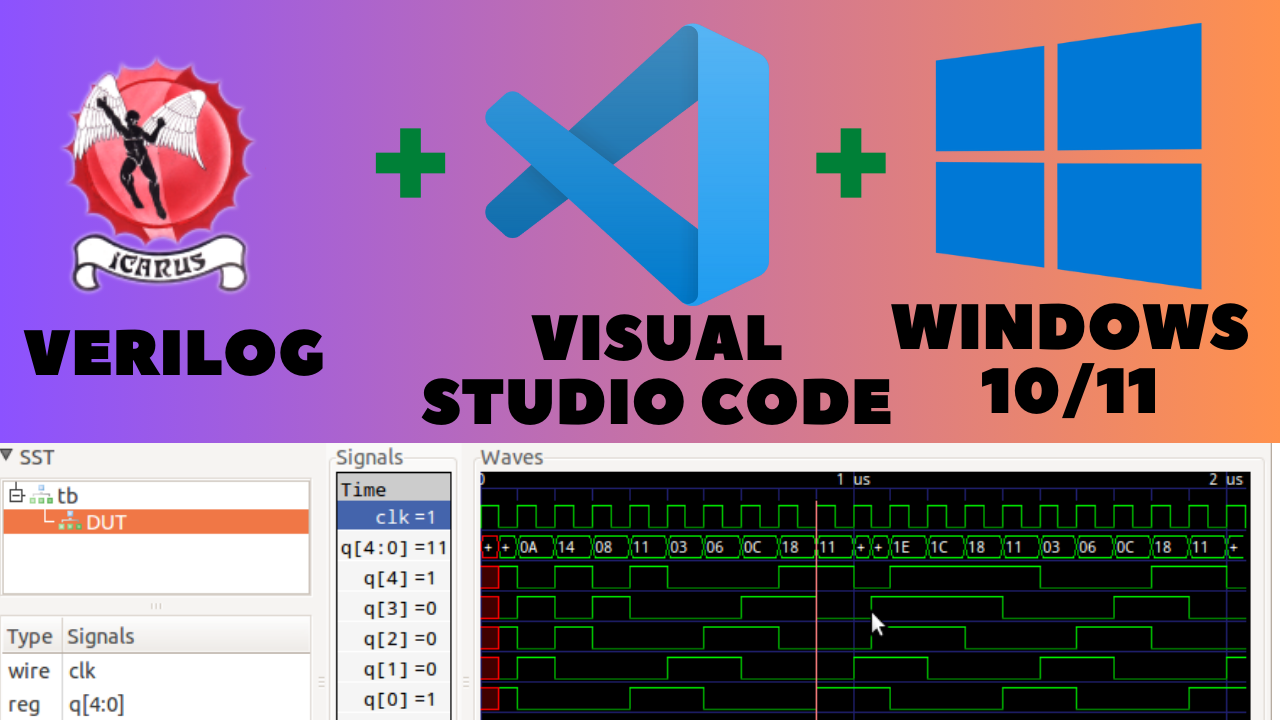

How to install Icarus Verilog to start coding Verilog:

When it comes to learning Verilog, many of the popular tools like Xilinx, Intel Quartus Prime, Vivado Design Suite, and ModelSim are often the first names that come to mind. However, these tools can be quite heavy, usually more than 20 GBs and in some cases near to 100 GB, consuming significant system resources, and they may not always be free or fully compatible with the latest versions of Windows, such as Windows 11.

If your primary goal is to learn Verilog without the overhead of these resource-intensive tools, there’s a much simpler solution which is Icarus Verilog —a lightweight tool that’s incredibly easy to install, occupies just a few hundred megabytes including all dependencies, and is fully compatible with Windows 11. A couple of 100’s of MBs for Icarus Verilog versus more than 20 GBs in case of many commercial tools, is a huge difference. Icarus Verilog is the perfect choice for anyone looking to master Verilog without the hassle.

In this article, we will see how to:

- Download and install the Icarus Verilog

- Write Verilog code using Icarus Verilog

- Write the test bench for our design

- View the signal waveforms.

- Integrate Icarus Verilog with Visual Studio Code IDE, for a smooth and professional code-writing experience.

To install Icarus Verilog, one prerequisite is having the C compiler (GCC) installed on your system. If you have the C compiler installed on your system, you can continue for the next steps. If C compiler is not installed, please refer to this article in which all steps are shown to install the C compiler and integrated that with Visual Studio Code.

Two methods of installing Icarus Verilog:

We will explore two methods to install Icarus Verilog:

- Using installer from the website

- Using MSYS2 (MSYS2 is a software installation and building platform for windows. MSYS2 can handle the dependencies and updates very effectively)

1. Installation using Installer from Website:

Go to the link: https://bleyer.org/icarus/

Choose the latest stable release available there. At present the latest stable release is shown here:

Run the installer and follow the simple steps to install. It will be installed in the C drive. Don’t forget to install GTKWave which will be used to view the waveforms, when asked in a window as shown:

After the installation, we should verify if the Icarus Verilog has been successfully installed. For that, we need to open the command prompt. Go to the Windows Search Bar and type CMD and hit enter. The command prompt window will open as shown below:

Write the following command:

>iverilog

You might see the error that iverilog is not recognize as internal or external command, as shown below:

The reason is that Icarus Verilog was installed in the C drive:

And inside iverilog folder there is a folder bin, inside which we have the iverilog application.

So we need to tell Windows about this path (C:\iverilog\bin) so that it is accessible in the whole system.

Now go to Windows Search bar and search for “Environment Variables” and click “Edit the system environment variables”. This window will open:

Click “Environment Variables” at the bottom of the above window. A new window will open and we need to edit the path variable in the lower section:

Select the Path variable and Click “Edit” to edit it. This window will open:

Here click “New” to add a new path and paste the path C:\iverilog\bin. Then Click “OK” a couple of times.

Now you can open the command prompt again (using CMD in Windows search bar) and verify the installation of Icarus Verilog with this command:

>iverilog

Now you should get the information similar to this:

We can also view the version of Icarus Verilog installed by the command

>iverilog -V

The output will show full details of Icarus Verilog along with the version installed.

2. Installation using MSYS2:

Now let’s see how to install Icarus Verilog by using MSYS2. First, you should have MSYS2 installed and for that you can follow the same previous article.

With MSYS2 installed, go to the Windows Search Bar and look for MSYS2MinGW64. A command-based interface will open. The first step is always updating the package databases using pacman package manager. Use this command:

$ pacman -Syu

It will ask for yes or no as [Y/n], then press Y.

Now to install Icarus Verilog, use this command.

$ pacman -S mingw-w64-x86_64-iverilog

We also need to install GTK Wave for the Signal Waveforms. For that, we will use this command:

$ pacman -S mingw-w64-x86_64-gtkwave

To verify the installation, use the command:

$iverilog -V

You should get the version information. The command we used will automatically install the latest version. Also verify the installation of GTK-Wave with the following command:

$gtkwave

It should open the GTK-Wave window as shown below, which means it has been installed.

How to write Verilog Codes:

First, we will see the method where we can write the code on simple text files and then we will integrate Icarus Verilog with Visual Studio Code IDE for better experience.

Use the following steps to write and execute the Verilog Codes in the text file.

Create a Verilog File:

- Go to the folder where you want to keep the files e.g. D:\VerilogCodes

- Create a new text file and name it something like test.v where the extension V is for the Verilog files.

- One very important point here is that you go to “View” tab on your Folder and select the option to view the file name extension.

- You would see the file name as test.v.txt which means the format is still .txt. Remove that .txt and ignore any warning. Now the file will be a Verilog extension file.

- Open the file in notepad where we can type the code.

- Copy this basic “Hello World” program in that file. This code is very basic code which simply displays “Hello World” on the screen.

module hello;

initial

begin

$display(“Hello, World”);

$finish ;

end

endmodule

Compile and Run the Verilog file:

It is all command base. You need to open the command prompt or better on MSYS2. For MSYS2, search for MSYS2 MinGW64 on the Windows Search Bar and MSYS2 command prompt will open.

Use the following steps to compile and run the code:

- The first step will be changing the directory to the one having the source file. Use the command cd to change directory followed by the path of the folder as (assuming the path is D:\VerilogCodes):

$ cd/d/VerilogCodes

- To compile the source file test.v available inside the selected folder use this command:

$ iverilog -o test.vvp test.v

(here -o means the output file and we specified the name of the output file as test.vvp. The name is preferably same as of the original source file i.e. test and the extension is VVP which is an intermediate file containing the compiled simulation code. Then we specify the source file which we are compiling i.e. test.v)

- The above command should not generate any error which means the code has been compiled correctly.

- If you go to the folder, you should see the output file test.vvp generated there.

The next step is running the VPP file. For that use the following steps:

- To run the vvp file you created in last step use this command on MSYS2 command prompt:

$ vvp test.vvp

And you should get the Hello World printed on the output as shown here:

This was the basic testing. Now let’s do something meaningful and also create the test bench and the waveforms.

Full Adder with Test Bench and Waveforms:

Let’s create a Full Adder circuit code and then create the test bench for it and also view the wave forms. Follow these steps:

Create Source Module:

- Create a file fullAdder.v

- Copy this code:

`timescale 1ns / 1ps

module full_adder (

input a,

input b,

input c_in,

output wire sum,

output wire carry_out

);

// Assign sum using XOR for efficient bitwise addition

assign sum = a ^ b ^ c_in;

// Assign carry based on two-bit product terms for clarity

assign carry_out = (a & b) | (a & c_in) | (c_in & b);

endmodule

This module has three inputs (a, b, c_in) and two outputs (sum and carry_out). The outputs sum and carry_out are as per the full adder equations.

- One important point to mention here is that the name of the module is “full_adder” while the file name is fullAdder.v without any space or underscore. The file name and the module names are different. To compile and use the file we will have to use the file name i.e. fullAdder.v while to use the module in some other module like the test bench, we will use the module name i.e. full_adder. The naming conventions are just personal preferences.

- Now compile the full adder Verilog file using this command:

$ iverilog -o fullAdder.vvp fullAdder.v

- There should not be any error and the output file fullAdder.vvp should have been generated in the folder.

- You may run the VVP file with the command:

> vvp fullAdder.vvp

But there will be no output since we did not display anything.

Create Test Bench:

Now let’s do the next important step of creating and executing the test bench for the full adder. A test bench in Verilog is another Verilog program which verifies the functionality of the design. Follow these steps:

- Create the Verilog file for the test bench and name it as fullAdderTB.v

- Copy this code:

`timescale 1ns / 1ps

module tb_full_adder;

// Declare testbench signals

reg a, b, c_in;

wire sum, carry_out;

// Instantiate the full adder module

full_adder dut (a, b, c_in, sum, carry_out);

// Apply test stimulus

initial begin

$display(“Testing Full Adder”);

$monitor(“a = %b, b = %b, c_in = %b, sum = %b, carry_out = %b”, a, b, c_in, sum, carry_out);

// Apply various test cases

a = 0; b = 0; c_in = 0; #10; // Expect sum = 0, carry_out = 0

a = 0; b = 0; c_in = 1; #10; // Expect sum = 1, carry_out = 0

a = 0; b = 1; c_in = 0; #10; // Expect sum = 1, carry_out = 0

a = 0; b = 1; c_in = 1; #10; // Expect sum = 0, carry_out = 1

a = 1; b = 0; c_in = 0; #10; // Expect sum = 1, carry_out = 0

// … Add more test cases as needed

$finish;

end

endmodule

- Note that the name of this module we specified is “tb_full_adder” which is different from the file name i.e. fullAdderTB.v

- In the code we are instantiating an instance of full adder as: full_adder dut (a, b, c_in, sum, carry_out). The dut is just the variable name; it could be anything. The dut means design under test. Then in the code there is a block inside which we are displaying a simple message followed by a few variable values we want to see, using the monitor function. The monitor function displays all the values specified whenever there is some change in any of the variable values specified. And finally, we are assigning different values to input variables and would like to see the values of output variables.

- After creating the test bench file we need to compile that using this command on MSYS2 command window:

$ iverilog -o fullAdderTB.vcd fullAdderTB.v fullAdder.v

The extension VCD is Value Change Dump file that logs signal value changes over time during a Verilog simulation for waveform analysis and debugging. As the source file, we will have to specify the test bench file but also the full adder module file.

- There should be no error and we should have the VCD file generated in the folder.

- You can run the VCD file on the command prompt as:

$ vvp fullAdderTB.vcd

You will see the output as where we have the display message and then the five variables we specified in the monitor function every time some value is updated:

You can verify for any set of three inputs, the carry and sum are correct.

- We got the correct output of the test bench but we need to view the signal values as waveform. For that we first need one change in the test bench code. Before applying different simulation values, we need a couple of lines:

// Dumpfile and dumpvars for waveform generation

initial begin

$dumpfile(“fullAdderTB.vcd”); // Specify dump file name

$dumpvars(0, tb_full_adder); // Dump all signals in the testbench

end

We need to add the above lines in the test bench code just after the line full_adder dut (a, b, c_in, sum, carry_out);

Let’s discuss the purpose of the two lines we added. We are specifying a file where the signal values will be saved:

- The first is the dumpfile function where the name of the file should be specified that will hold the values of different variables: $dumpfile(“fullAdderTB.vcd”); We specified the output VCD file.

- The second line is dumpvars function where we specified the name of the module of the test bench meaning all variables of this test bench will be dumped.

- Compile the test bench again since the code has been updated.

$ iverilog -o fullAdderTB.vcd fullAdderTB.v fullAdder.v

- You can run the VCD file if you wish but we want to view the signal waveforms.

- Open the GTK-Wave with the command:

$ gtkwave

This will open the GTK-Wave window.

- You need to drag the VCD file onto this window.

- Double-click the signals from the signals section to view.

- You might initially see the flat lines as shown here:

- Use the Zoom buttons and preferably “Fit to Window” option and you should be able to see the waveforms as:

Integrating Icarus Verilog with Visual Studio Code (VSC):

You see coding on the text files is very cumbersome and it will be good if we could code this in some IDE like Visual Studio Code. To add the Verilog support, go to the extension tab and search for Verilog. You will see a bunch of extensions. You can choose any of these based on ratings and downloads.

After installing the extension you will get the proper IntelliSense help as well.

To run the code, you will have to use the commands on the terminal. For that go to the Menu bar option as TerminalàNew Terminal. It will open the terminal in VSC where you can write all the commands we discussed previously.

All steps are shown in this YouTube video.